# ECE 105: Introduction to Electrical Engineering

Lecture 5

Device 1

Yasser Khan

Rehan Kapadia

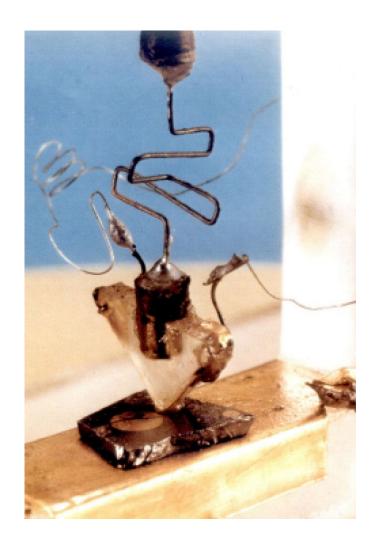

# The First Transistor

# 1956 Physics Nobel Prize

"for their researches on semiconductors and their discovery of the transistor effect"

#### William Bradford Shockley

O 1/3 of the prize

USA

Semiconductor Laboratory of Beckman Instruments, Inc. Mountain View, CA, USA

#### John Bardeen

O 1/3 of the prize

USA

University of Illinois Urbana, IL, USA

Walter Houser Brattain

O 1/3 of the prize

USA

Bell Telephone Laboratories Murray Hill, NJ, USA

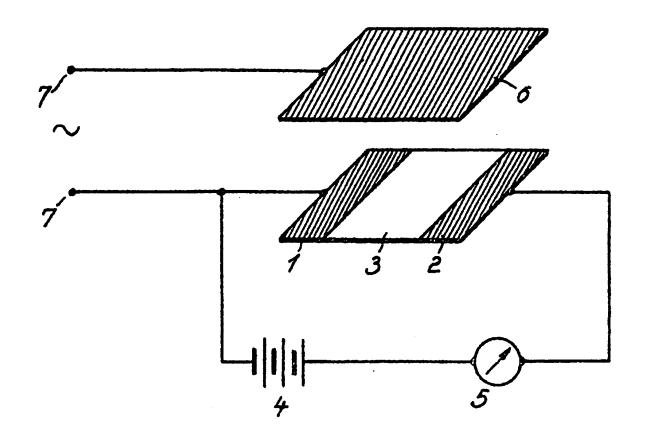

## Invention of the Field-Effect Transistor

In 1935, a British patent was issued to Oskar Heil. A working MOSFET was not demonstrated until 1955.

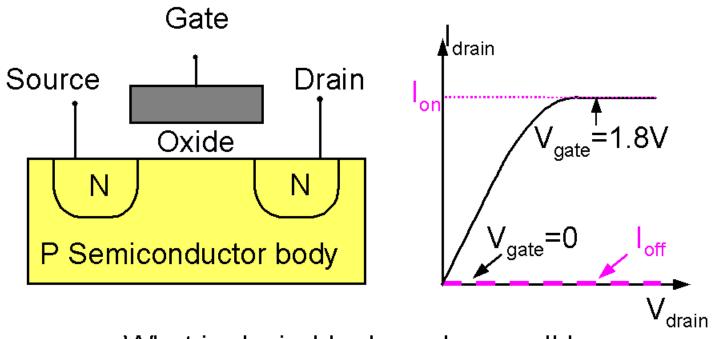

An electric field is applied normal to the surface of the semiconductor (by applying a voltage to an overlying electrode), to modulate the conductance of the semiconductor

→ Modulate drift current flowing between 2 contacts ("source" and "drain") by varying the voltage on the "gate" electrode

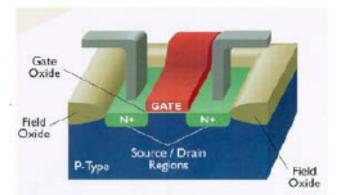

N-channel MOSFET:

### Introduction to the MOSFET

### Basic MOSFET structure and IV characteristics

What is desirable: large  $I_{on}$ , small  $I_{off}$

# Introduction to the MOSFET

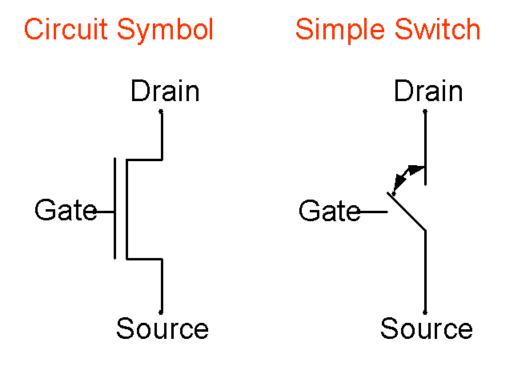

Two ways of representing a MOSFET:

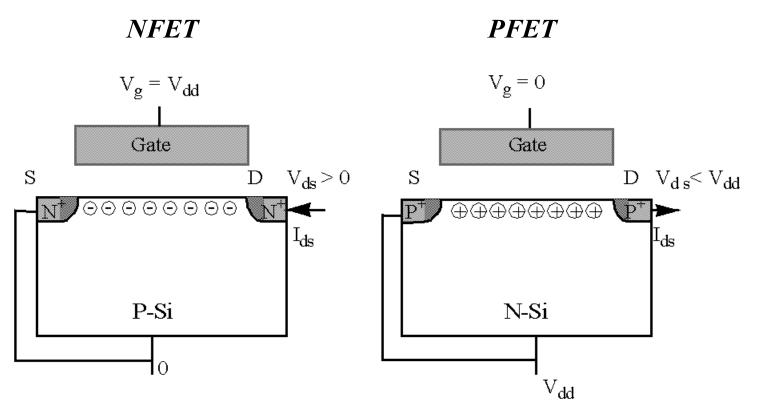

### N-channel vs. P-channel

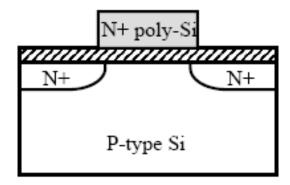

#### NMOS

- For current to flow, V<sub>GS</sub> > V<sub>T</sub>

- Enhancement mode: V<sub>⊤</sub> > 0

- Depletion mode: V<sub>T</sub> < 0</li>

- Transistor is ON when V<sub>G</sub>=0V

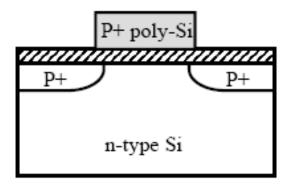

#### PMOS

- For current to flow, V<sub>GS</sub> < V<sub>T</sub>

- Enhancement mode: V<sub>T</sub> < 0</li>

- Depletion mode:  $V_T > 0$

- Transistor is ON when V<sub>G</sub>=0V

# Complementary MOSFETs (CMOS)

When  $V_g = V_{dd}$ , the NFET is on and the PFET is off. When  $V_g = 0$ , the PFET is on and the NFET is off.

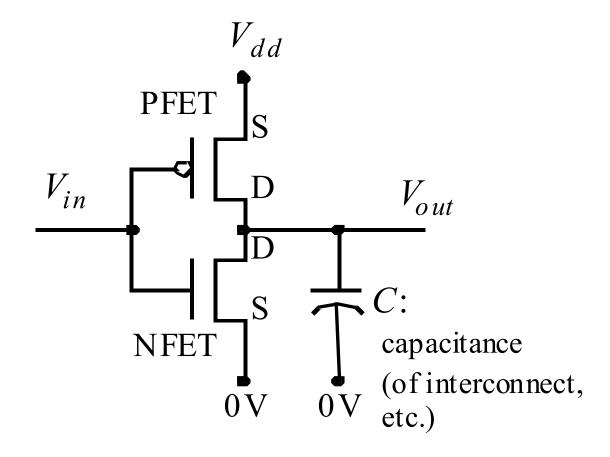

# CMOS (Complementary MOS) Inverter

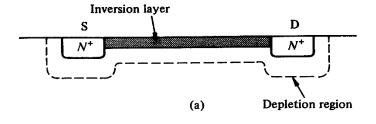

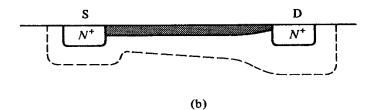

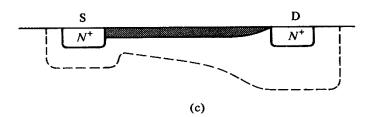

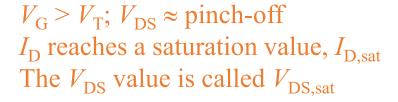

# Qualitative discussion: n-MOSFET

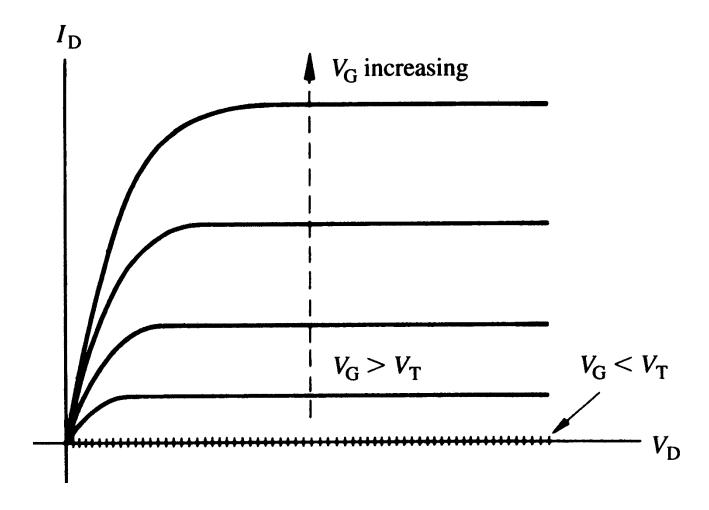

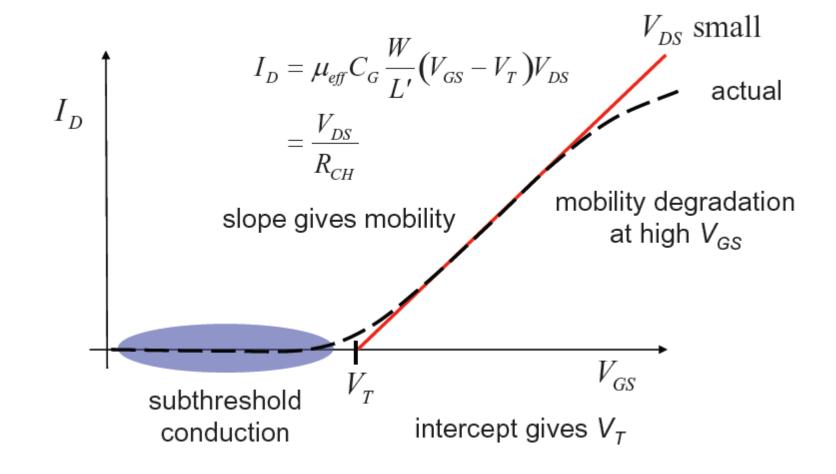

$V_{\rm G} > V_{\rm T}; V_{\rm DS} \text{ small,} > 0$  $I_{\rm D}$  increases with  $V_{\rm DS}$ , but rate of increase decreases.

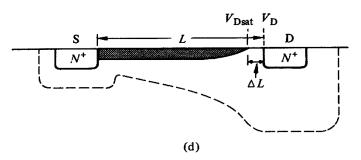

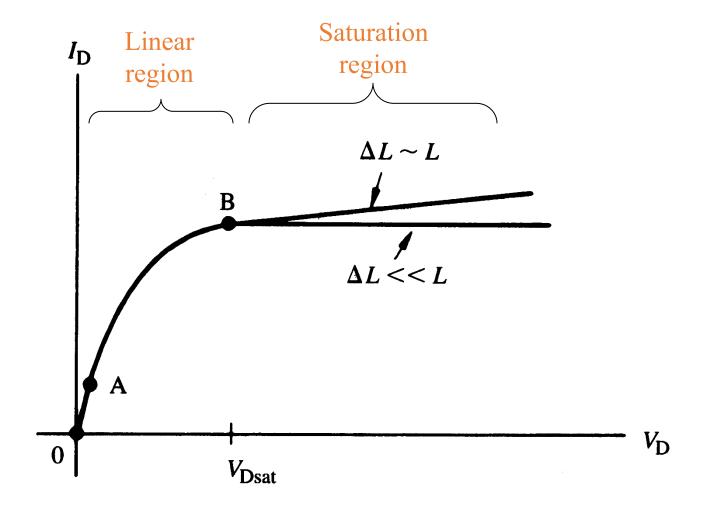

$V_{\rm G} > V_T$ ;  $V_{\rm DS} > V_{\rm DS,sat}$  $I_{\rm D}$  does not increase further, saturation region.  $I_{\rm D}$ - $V_{\rm DS}$  characteristics expected from a long channel ( $\Delta L << L$ ) MOSFET (n-channel), for various values of  $V_{\rm G}$

# $I_D$ - $V_{DS}$ characteristics for n-MOSFET

# Quantitative $I_D$ - $V_{DS}$ Relationships – $1^{st}$ attempt "Square Law"

$$I_{\rm D} = \frac{Z\mu_{\rm n}}{L} C_{\rm ox} \left[ (V_{\rm G} - V_{\rm T}) V_{\rm DS} - \frac{V_{\rm DS}^2}{2} \right] \quad 0 < V_{\rm DS} < V_{\rm DS,sat} \; ; \quad V_{\rm G} > V_{\rm T}$$

$I_{\rm D}$  will increase as  $V_{\rm DS}$  is increased, but when  $V_{\rm G} - V_{\rm DS} = V_{\rm T}$ , pinchoff occurs, and current saturates when  $V_{\rm DS}$  is increased further. This value of  $V_{\rm DS}$  is called  $V_{\rm DS,sat}$ . i.e.,  $V_{\rm DS,sat} = V_{\rm G} - V_{\rm T}$  and the current when  $V_{\rm DS} = V_{\rm DS,sat}$  is called  $I_{\rm DS,sat}$ .

$$I_{\text{D,sat}} = \frac{Z \mu C_{\text{ox}}}{2L} (V_{\text{G}} - V_{\text{T}})^2$$

$V_{\text{D}} > V_{\text{DS,sat}}$  ;  $V_{\text{G}} > V_{\text{T}}$

Here,  $C_{\text{ox}}$  is the oxide capacitance per unit area,  $C_{\text{ox}} = \varepsilon_{\text{ox}} / x_{\text{ox}}$

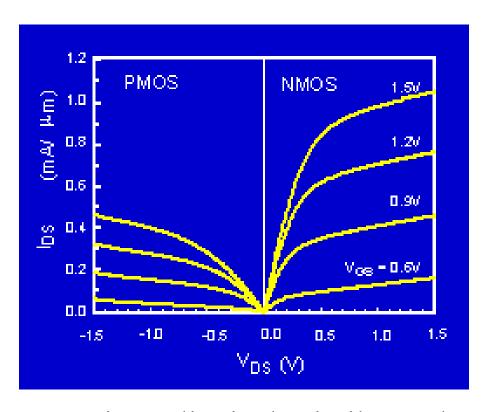

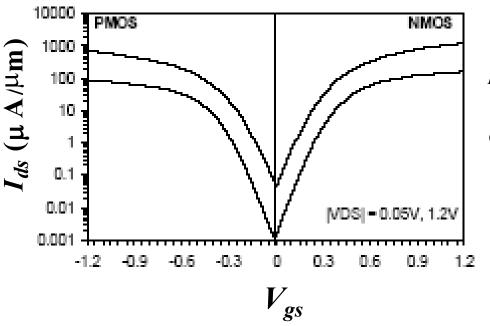

# P-MOSFET N-MOSFET IV Characteristics

The PMOS IV is qualitatively similar to the NMOS IV, but the current is about half as large. Why?

### Threshold and Subthreshold

### Subthreshold Current

• The leakage current that flows at  $V_g < V_t$  is called the subthreshold current. Previously we had assumed that current is zero, but in reality that's not the case.

90nm technology.

Gate length: 45nm for NMOS, 50nm for PMOS

• The current at  $V_{gs}=0$  and  $V_{ds}=V_{dd}$  is called  $I_{off}$ .